#### Практическое занятие №18

#### КЛЮЧ НА БИПОЛЯРНОМ ТРАНЗИСТОРЕ

## Теоретические сведения

## АНАЛОГОВЫЙ КЛЮЧ

При работе в ключевом режиме транзистор может находиться в одном из двух устойчивых состояний — выключенном (режим отсечки) и включенном (режим насыщения).

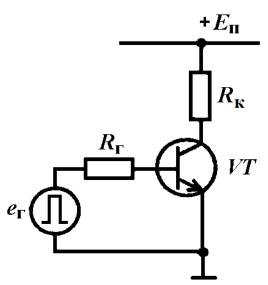

Рис. 1. Ключ на биполярном транзисторе

В режиме отсечки ток базы  $I_6=0$ , коллекторный ток  $I_{\rm K}\approx 0$ , а коллекторное напряжение  $U_{\rm K9}=E_{\rm II}-I_{\rm K}R_{\rm K}\approx E_{\rm II}$ . На практике режим отсечки реализуется при  $E_{\rm I}=0$  или при отрицательном входном напряжении  $E_{\rm I}$ .

В режим насыщения транзистор переводится положительным входным напряжением  $E_{\Gamma}$ . При этом напряжение  $U_{\kappa_3}$  принимает свое минимальное значение  $U_{\kappa_3 \text{ нас}}$ , обычно в несколько десятых долей вольта, т.е. в расчетах часто можно принять  $U_{\kappa_3 \text{ нас}} \approx 0$ , тогда ток коллектора равен  $I_{\kappa} = I_{\kappa \text{ нас}} \approx E_{\kappa}/R_{\kappa}$ .

Для того чтобы транзистор вошел в режим насыщения, в его базу необходимо

подать ток, больший, чем необходимо для протекания тока  $I_{\text{к нас}}$ , т.е.

$$I_6 > I_{\text{K Hac}} / \beta. \tag{1}$$

То, насколько сильно  $I_6$  больше, чем  $I_{\kappa\,\text{нас}}$  /  $\beta$ , т.е. насколько «надежно» насыщен транзистор, характеризуется коэффициентом насыщения транзистора:

$$K_{\text{Hac}} = \beta I_{\text{f}} / I_{\text{k Hac}}. \tag{2}$$

Из-за того, что у реальных транзисторов существует значительный разброс параметра  $\beta$  (который к тому же снижается при входе транзистора в режим насыщения), стараются обеспечить значение расчетного  $K_{\text{нас}}$  в несколько единиц (часто в пределах 5-10), чтобы реальное значение  $K_{\text{нас}}$  в худшем случае было больше 1.

Необходимую величину тока базы определяет амплитуда источника  $E_{\rm r}$ :

$$I_{\rm G} = (E_{\rm \Gamma} - U_{\rm 69 \; Hac})/R_{\rm \Gamma},\tag{3}$$

где  $U_{69 \text{ нас}} \approx 0,6-0,8 \text{ B}.$

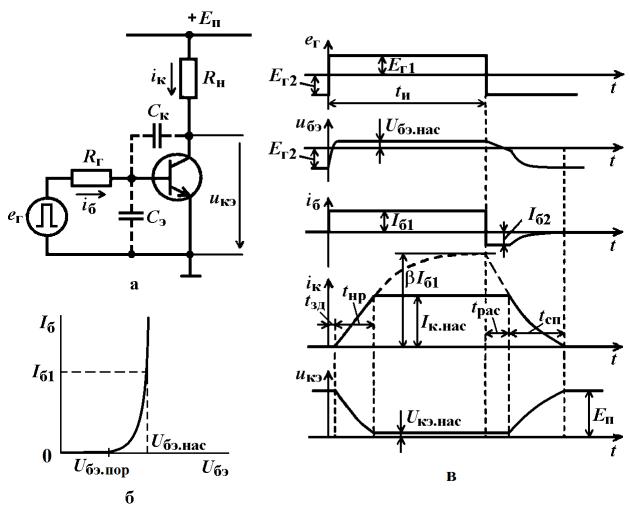

Длительности переходных процессов, протекающих в транзисторе при его переключении из режима отсечки в режим насыщения и наоборот, во многом определяются емкостями его переходов (рис. 2).

Так, задержка фронта при включении обусловлена перезарядом входной емкости транзистора  $C_{\rm Bx}$ , которая равна сумме барьерных емкостей коллекторного  $C_{\kappa}$  и эмиттерного  $C_{\mathfrak{p}}$  переходов. Изначально емкость  $C_{\mathtt{BX}}$ отрицательного напряжения  $u_{69}=E_{r2}$ . Этап заканчивается, когда  $C_{\text{вх}}$  заряжается до напряжения  $U_{\text{бэ.пор}} = (0,5-0,7)$  В, при котором транзистор открывается. Длительностью этапа задержки на практике онжом пренебречь, поскольку намного меньше длительности она следующего этапа.

Рис. 2. Схема простейшего ключа на биполярном транзисторе с ОЭ и резистивной нагрузкой (а), входная ВАХ транзистора (б) и временные диаграммы токов и напряжений (б). Барьерные емкости  $C_9$ ,  $C_{\kappa}$  условно вынесены за пределы транзистора

На этапе **нарастания** тока  $t_{\rm hp}$  транзистор работает в активном (усилительном) режиме, ток коллектора  $i_{\rm k}$  нарастает до величины  $I_{\rm k\, hac}$ . Напряжение на транзисторе за это время падает с первоначального значения  $E_{\rm II}$  до  $U_{\rm k9\, hac}$ , поскольку в усилительном режиме между током и напряжением выполняется соотношение  $U_{\rm k9} = E_{\rm II} - I_{\rm k} R_{\rm k}$ , т.е. рост тока приводит к уменьшения напряжения.

Длительность этапа  $t_{\rm hp}$  определяется как

$$t_{\rm hp} = \tau_{_{9KB}} \ln \frac{\beta I_{_{61}}}{\beta I_{_{61}} - I_{_{K.Hac}}} = \tau_{_{9KB}} \ln \frac{K_{_{Hac}}}{K_{_{Hac}} - 1}$$

(4)

где  $\tau_{3KB} = \tau_{\beta} + (1 + \beta) R_H C_K - 3$ квивалентная постоянная времени транзистора при его включении с ОЭ, учитывающая время жизни носителей в активном режиме  $\tau_{\beta}$  и перезаряд емкости  $C_K$  при изменении напряжения  $U_{KS}$ .

Время жизни носителей

$$\tau_{\beta} = \frac{1}{2\pi f_{\beta}},\tag{5}$$

где  $f_{\beta}$  – граничная частота транзистора в схеме с ОЭ, на которой модуль коэффициента передачи

$$|\beta(f)| = \frac{\beta_0}{\sqrt{1 + (f/f_\beta)^2}} \tag{6}$$

снижается в  $\sqrt{2}$  раз от первоначального значения  $\beta_0$  на нулевой частоте (на постоянном токе).

Часто в справочных данных транзистора указывается значение модуля его коэффициента передачи в схеме с ОЭ  $\left|\beta(f^*)\right|$  на частоте  $f^*$ . В этом случае значение граничной частоты

$$f_{\beta} = \left| \beta \left( f^* \right) \right| \cdot f^* / \beta_0 . \tag{7}$$

После подачи в базу запирающего тока с амплитудой  $I_{62}$  начинается процесс выключения транзистора, состоящий из двух этапов: рассасывания длительностью  $t_{\rm pac}$  и спада коллекторного тока длительностью  $t_{\rm cn}$ .

Как уже было сказано, для режима насыщения транзистора характерно то, что в базу подается ток больше, чем необходимо для поддержания  $I_{\kappa}$  нас. Для того чтобы перевести транзистор из состояния насыщения снова в активный режим, необходимо удалить избыточный заряд, накопленный в базе. Этот этап называется этапом рассасывания. Длительность этапа оценивается как

$$t_{\text{pac}} = \tau_{\beta} \ln \frac{I_{61} + |I_{62}|}{I_{\text{K Hac}} / \beta + |I_{62}|} = \tau_{\beta} \ln \frac{K_{\text{Hac}} I_{\text{K.Hac}} + \beta |I_{62}|}{I_{\text{K Hac}} + \beta |I_{62}|},$$

(8)

где  $I_{62} = E_{\Gamma 2}/R_{\Gamma}$ .

Знак модуля означает, что нас интересует амплитуда перепада токов.

Напряжение на транзисторе  $U_{\mbox{\tiny K9}}$  на этом этапе не меняется, оставаясь равным  $U_{\mbox{\tiny K9 Hac}}$ , т.е. «внешне» транзистор остается открытым.

На **этапе спада**  $t_{\text{сп}}$  транзистор работает в активном режиме, и уменьшение накопленного в базе заряда неосновных носителей сопровождается уменьшением коллекторного тока. Напряжение  $U_{\text{кэ}}$  на этом этапе растет с  $U_{\text{кэ}}$  нас до  $E_{\text{п}}$ . Длительность этапа:

$$t_{\rm cii} = \tau_{_{\rm 3KB}} \ln \left( 1 + \frac{I_{_{\rm K,Hac}}}{\beta |I_{62}|} \right).$$

(9)

# ЛОГИЧЕСКИЙ КЛЮЧ

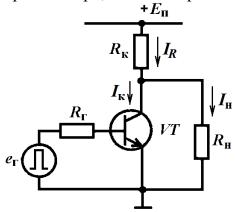

Помимо временных параметров, транзисторный ключ характеризуется **нагрузочной способностью**. Особенно это важно для логических ключей, т.е. элементов цифровой техники. Под нагрузочной способностью обычно подразумевают максимальную величину тока нагрузки, который может выдать на выходе ключ (цифровая микросхема).

Для показанной на рис. З схемы в случае насыщенного состояния транзистора, когда напряжение  $U_{\text{кэ}} = U_{\text{кэ} \text{ нас}} \approx 0$ , ток нагрузки  $I_{\text{н}} = U_{\text{кэ}} / R_{\text{н}}$ , т.е.

Рис. 3. Ключ с нагрузкой

в данном случае равен 0. Следовательно, этот режим нас не интересует с точки зрения нагрузочной способности ключа.

В режиме отсечки, когда транзистор закрыт и его ток  $I_{\rm K} \approx 0$ , через  $R_{\rm K}$  течет  $I_R = I_{\rm H}$ , тогда

$$U_{\kappa_9} = E_{\Pi} - I_{\mathrm{H}} R_{\kappa}, \qquad (10)$$

т.е. оно уже не равно напряжению  $E_{\rm II}$ . Чем больше потребляемый нагрузкой ток (т.е. чем меньше сопротивление нагрузки  $R_{\rm H}$ ), тем меньше  $U_{\rm K3}$ .

Для логического ключа важно сохранение достаточно высокого уровня выходного напряжения в закрытом состоянии транзистора, чтобы однозначно интерпретировать это напряжение как напряжение высокого уровня, т.е. «логическую единицу». С учетом падения напряжения на резисторе  $R_{\kappa}$  при протекании через него тока нагрузки уровни напряжения логической «1» задают в интервале. Например, для логических ключей на биполярных транзисторах это обычно 2,7 – 5 В (где 5 В – это величина  $E_{\pi}$ ). Соответственно, напряжение логического «0» также задается в интервале, в данном случае это будет 0-0.5 В.

Очевидно, что ток нагрузки в выражении (10) не должен превысить величину, при которой напряжение  $U_{\kappa_9}$  равно минимально приемлемому уровню для логической «1», т.е. в данном случае 2,7 В.

## Задачи для решения

**Задача 1.** Рассчитать амплитуду отпирающего напряжения  $E_{\Gamma}$ , необходимого для коэффициента насыщения показанного на рис. 1 транзистора  $K_{\text{нас}} = 6$ , если известно, что  $E_{\Pi} = 15$  B,  $R_{K} = 100$  Ом,  $R_{\Gamma} = 30$  Ом,  $U_{\text{бэ.нас}} = 0.8$  B,  $\beta = 25$ .

**Задача 2.** Определите время включения биполярного транзистора в приведенной на рис. 1 схеме, если  $E_{\rm II}=50~{\rm B},\,R_{\rm K}=30~{\rm OM},\,\beta=15,$  отпирающее напряжение  $E_{\rm II}=3~{\rm B},\,$  запирающее напряжение  $E_{\rm II}=-3~{\rm B},\,R_{\rm II}=5~{\rm OM},$  граничная частота транзистора  $f_{\beta}=2~{\rm M}\Gamma$ ц, барьерная емкость коллекторного перехода  $C_{\rm K}=2~{\rm H}\Phi,\,U_{\rm бо, Hac}=0.7~{\rm B}.$

<u>Примечание:</u> временем включения транзисторного ключа называется сумма длительностей этапов задержки и нарастания. С учетом допущения, что  $t_{\rm 3д} << t_{\rm hp}$ ,  $t_{\rm вкл} \approx t_{\rm hp}$ .

Задача 3. Определите время выключения биполярного транзистора в приведенной на рис. 1 схеме, если  $E_{\Pi}=30$  В,  $R_{\kappa}=20$  Ом,  $\beta=30$ , отпирающее напряжение  $E_{\Gamma 1}=2$  В, запирающее напряжение  $E_{\Gamma 2}=-2$  В,  $R_{\Gamma}=10$  Ом,  $U_{69,\text{нас}}=0,6$  В, барьерная емкость коллекторного перехода  $C_{\kappa}=5$  нФ. Модуль коэффициента передачи транзистора в схеме с ОЭ  $|\beta(f)|=10$  на частоте f=5 МГц.

<u>Примечание:</u> временем выключения транзисторного ключа называется сумма длительностей этапов рассасывания и спада.

**Задача 4.** Для схемы ключа на рис. 3 определить минимальное значение сопротивления нагрузки, если известно, что  $E_{\Pi}=5$  B,  $U_{\Pi}=2,7$  B,  $R_{K}=1$  кОм.